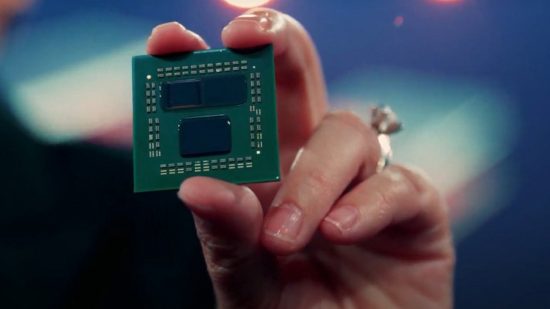

At Computex 2021 on 1 June, AMD surprised those watching online with the revelation that it had developed a Zen 3 design with a stacked L3 cache, strapping an extra 64MB directly on top of the 32MB inside each 8-core chip. AMD called this innovation 3D V-Cache and showed off a Ryzen 5900X featuring it, stating it would give a 12-core or 16-core Ryzen 9 CPU a total L3 cache of 192MB.

What’s more, an evaluation BIOS for the company’s EPYC server CPUs showed an option that implied four of these caches could be stacked four on top of each other. This means, in theory, that a 64-core CPU could have 2.3GB of L3 cache!

Huge ‘last level’ caches benefit compute-focused workloads by keeping more data closer to the processing cores. These caches won’t ever have the sheer capacity of main memory, but they’re much faster and have lower latency, so the CPU doesn’t have to wait.

AMD is claiming 2TB/sec of throughput and a 15 per cent performance increase on the same Zen 3 CPU, which is equal to an average CPU generational improvement itself.

However, there are still many unanswered questions, such as how much power it draws, whether the hot spots get worse and how often we’re really going to see that 15 per cent performance uplift. This 3D V-Cache is built using TSMC’s direct chip-to-chip stacking with ‘through-silicon-via’ (TSV) tech. TSV is absolutely leading-edge tech.

Intel’s 2019 Lakefield chip had another stacked design, which it branded Feveros. However, Intel’s technology uses micro-bumps of solder that, while advanced at the time, can only offer up to 400 connections/mm².

In comparison, AMD is claiming a 15x improvement using this chip-to-chip bonding, which equates to around 6,000 connections/mm². AMD is also mating two 7nm chips together, while Intel partnered a 10nm compute die with a much older 22nm I/O die.

To its credit, last year Intel stated it had test chips using similar chip-to-chip packaging technologies working in its labs, but it has yet to announce a product or even show the test chip working. AMD’s announcement has caught Intel napping, and it’s now under considerable pressure to demonstrate a competitive technology, because the strength of its claims is rapidly evaporating.

In AMD’s closing statements during the Computex stream, CEO Lisa Su noted that 3D V-Cache will be coming ‘later this year’. It’s been 18 months since its Zen 3-based CPUs launched, and Zen 4 won’t be ready until late 2022, so it’s likely we’ll see some refreshed Zen 3-based Ryzen chips with this tech this year, in an attempt to snatch the hype from Intel’s new 12th-gen Alder Lake chips.

However, the cost of implementing 3D V-Cache can’t be understated. It requires even more silicon than normal at a time when wafers are in exceptionally high demand, and uses a cutting-edge packaging technology that, by TSMC’s own admission, won’t be ready for mass production until next year.

I expect we’ll see 3D V-Cache limited to select products only – maybe even just a single flagship processor (at a premium price) to battle for the title of fastest CPU.

This matters, because even if AMD doesn’t sell many of these chips, the effect of being the best at the top affects the perception of all its CPUs down the product range, boosting sales. This CPU could be like one of the premium AMD FX CPUs of the early 2000s. Could they be making a comeback?